Page 1 sur 5

Certains téléphones ne permettent pas d'émettre un dièse pendant une seconde. Cette carte détecte donc un double dièse et réalise la même fonction que la carte de commande vocale.

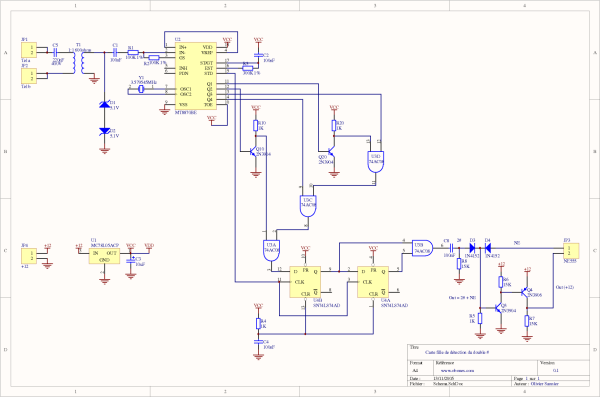

Schéma

Voici le schéma de principe. Les JP* ont les mêmes références que sur la carte mère 2Lignes1Tel.

Nomenclature

| Designator | Type | Valeur | Quantité |

| C3 | Cond. Pol. 25V | 10uF | 1 |

| C5 | Cond. 400V | 220nF | 1 |

| C1, C2, C4, C8 | Cond. 63V | 100nF | 4 |

| D1, D2 | Diode Zener | 5.1V | 2 |

| D3, D4 | Diode | 1N4152 | 2 |

| JP1, JP2, JP3, JP4 | Jumper 1x2 | 4 | |

| Q3, Q10, Q20 | Transistor NPN CMS | MMBT3904 | 3 |

| Q4 | Transistor PNP CMS | MMBT3906 | 1 |

| R1, R2 | Resistance axiale | 100K 1% | 2 |

| R3 | Resistance axiale | 300K 1% | 1 |

| R4, R5 | Resistance axiale | 1K | 2 |

| R10, R20 | Resistance CMS 0805 | 1K | 2 |

| R6, R7, R8 | Resistance axiale | 15K | 3 |

| T1 | Transformateur | 1:1 600 ohms | 1 |

| U1 | Reg. 5V | 78L05 TO-92 | 1 |

| U2 | Décodeur DTMF | MT8870CE (PDIP) | 1 |

| U3 | Quad And | 74xx08 CMS | 1 |

| U4 | Dual D type Flip Flop | 74xx74 CMS | 1 |

| Y1 | Quartz | 3.579545MHz | 1 |

Note: Si vous avez consulté cette page avant le 13 novembre 2005, les transistors étaient des JFET et étaient plus nombreux. Mais il manquait une résistance de pull down sur chacune des portes NON ce qui lors des tests à conduit à ce que les deux JFET conduisent en même temps d'où court-circuit. Je suis donc revenu à une configuration plus simple, à base de transistors bipolaires.